集成電路設(shè)計(jì)中的防DPA攻擊方法

隨著集成電路在安全關(guān)鍵領(lǐng)域(如金融、通信、國(guó)防)的廣泛應(yīng)用,其面臨的安全威脅日益嚴(yán)峻。差分功耗分析(DPA)攻擊作為一種高效的側(cè)信道攻擊手段,能夠通過(guò)分析設(shè)備運(yùn)行時(shí)的功耗變化來(lái)提取密鑰等敏感信息,對(duì)芯片安全構(gòu)成了嚴(yán)重威脅。因此,在集成電路設(shè)計(jì)階段融入防DPA攻擊的防護(hù)措施,已成為安全芯片設(shè)計(jì)的核心環(huán)節(jié)。

防DPA攻擊的集成電路設(shè)計(jì)方法主要從降低功耗與信息泄露的相關(guān)性、增加噪聲干擾以及采用安全的算法與架構(gòu)三個(gè)層面展開(kāi)。

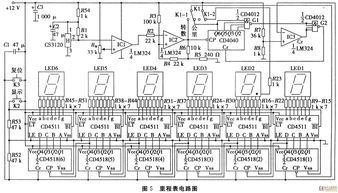

1. 電路級(jí)防護(hù):平衡功耗與隨機(jī)化

在電路級(jí),核心思路是消除或削弱功耗與所處理數(shù)據(jù)、操作之間的依賴(lài)關(guān)系。

- 功耗平衡邏輯:采用雙軌預(yù)充邏輯(如WDDL)等技術(shù),使電路無(wú)論處理“0”還是“1”,其充放電活動(dòng)與功耗都盡可能保持一致,從而使得功耗軌跡不泄露數(shù)據(jù)信息。

- 隨機(jī)化與掩碼技術(shù):通過(guò)在數(shù)據(jù)路徑上引入隨機(jī)掩碼,將真實(shí)的中間值與隨機(jī)數(shù)進(jìn)行組合運(yùn)算,使得功耗特征隨機(jī)化。攻擊者難以從混亂的功耗曲線(xiàn)中提取有效信息。這需要在算法、架構(gòu)和電路層面協(xié)同設(shè)計(jì),確保掩碼在運(yùn)算全程有效且最終能被安全移除。

- 異步電路設(shè)計(jì):異步電路沒(méi)有全局時(shí)鐘,其功耗在時(shí)間上分布更均勻,不易產(chǎn)生與時(shí)鐘同步的、規(guī)律性的功耗峰值,從而增加了DPA攻擊的難度。

2. 系統(tǒng)級(jí)防護(hù):噪聲注入與動(dòng)態(tài)調(diào)節(jié)

在更高的系統(tǒng)層級(jí),通過(guò)主動(dòng)控制來(lái)干擾攻擊者的測(cè)量與分析。

- 內(nèi)部噪聲發(fā)生器:在芯片內(nèi)部集成隨機(jī)噪聲源(如真隨機(jī)數(shù)發(fā)生器TRNG),并主動(dòng)將其注入電源網(wǎng)絡(luò)或時(shí)鐘網(wǎng)絡(luò)中,從而“淹沒(méi)”與操作相關(guān)的細(xì)微功耗信號(hào)。

- 動(dòng)態(tài)頻率與電壓調(diào)節(jié):動(dòng)態(tài)地改變芯片的工作頻率和核心電壓,使得功耗曲線(xiàn)的時(shí)序和幅度發(fā)生不可預(yù)測(cè)的變化,破壞DPA攻擊所需的多次測(cè)量間的對(duì)齊性。

- 功耗均衡調(diào)度:通過(guò)調(diào)度器,讓高功耗操作和低功耗操作交錯(cuò)執(zhí)行,或者讓不相關(guān)的模塊同時(shí)運(yùn)行,使得整體功耗輪廓趨于平坦。

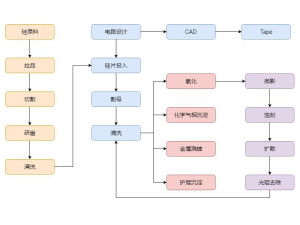

3. 算法與架構(gòu)級(jí)防護(hù)

這是最根本的防護(hù)層,旨在從計(jì)算本身降低信息泄露。

- 抗側(cè)信道攻擊的密碼算法實(shí)現(xiàn):在實(shí)現(xiàn)AES、RSA等密碼算法時(shí),采用諸如掩碼、隱藏等安全實(shí)現(xiàn)方式,確保即使功耗被采集,其與密鑰的關(guān)聯(lián)性也極低。

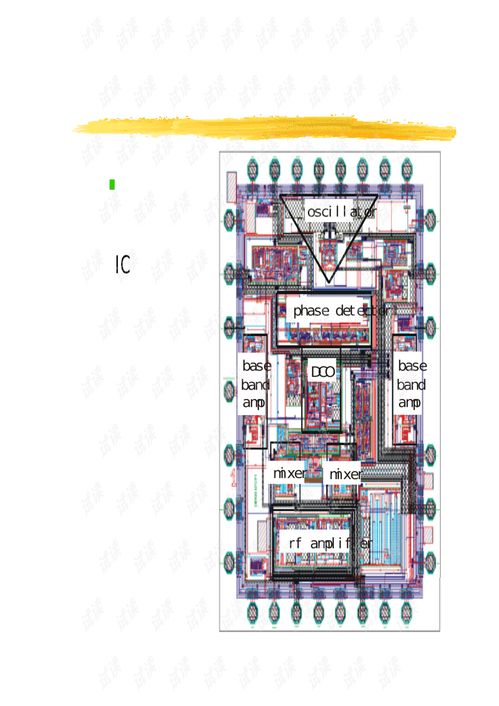

- 安全隔離與分區(qū):采用多核、TrustZone等硬件安全架構(gòu),將敏感計(jì)算與普通操作在物理或邏輯上隔離,限制攻擊者可觀(guān)測(cè)的功耗范圍。

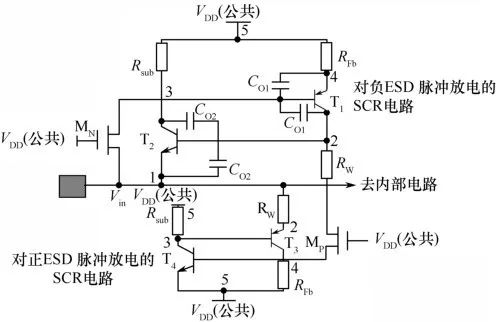

- 傳感器與主動(dòng)防御:集成溫度、電壓、頻率傳感器,用于檢測(cè)異常工作條件(可能預(yù)示著攻擊行為),并觸發(fā)重置、擦除密鑰等主動(dòng)防御機(jī)制。

設(shè)計(jì)挑戰(zhàn)與權(quán)衡

實(shí)施上述防護(hù)方法并非沒(méi)有代價(jià)。功耗平衡邏輯會(huì)顯著增加芯片面積和功耗;隨機(jī)化技術(shù)可能降低運(yùn)算速度并增加設(shè)計(jì)復(fù)雜性;噪聲注入本身也消耗能量。因此,集成電路安全設(shè)計(jì)是一個(gè)多維度的權(quán)衡過(guò)程,需要在安全性、性能(速度、功耗)、面積(成本)之間找到最佳平衡點(diǎn)。

結(jié)論

防御DPA攻擊需要一種貫穿集成電路設(shè)計(jì)全流程的、分層的安全設(shè)計(jì)理念。單一的防護(hù)措施難以應(yīng)對(duì)所有攻擊變種,因此必須結(jié)合電路級(jí)、系統(tǒng)級(jí)和算法架構(gòu)級(jí)的多種技術(shù),構(gòu)建縱深防御體系。隨著攻擊技術(shù)的不斷演進(jìn),防DPA攻擊的設(shè)計(jì)方法也需持續(xù)創(chuàng)新與改進(jìn),通過(guò)系統(tǒng)性的防護(hù)策略,在芯片的根源上筑牢安全防線(xiàn),確保敏感信息即使在物理可觸及的環(huán)境下也能得到有效保護(hù)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.jnqfy.cn/product/68.html

更新時(shí)間:2026-03-23 07:22:04